# Scalable energy-efficient magnetoelectric spin-orbit logic

Sasikanth Manipatruni<sup>1\*</sup>, Dmitri E. Nikonov<sup>1</sup>, Chia-Ching Lin<sup>1</sup>, Tanay A. Gosavi<sup>1</sup>, Huichu Liu<sup>2</sup>, Bhagwati Prasad<sup>3</sup>, Yen-Lin Huang<sup>3,4</sup>, Everton Bonturim<sup>3</sup>, Ramamoorthy Ramesh<sup>3,4,5</sup> & Ian A. Young<sup>1</sup>

Since the early 1980s, most electronics have relied on the use of complementary metal-oxide-semiconductor (CMOS) transistors. However, the principles of CMOS operation, involving a switchable semiconductor conductance controlled by an insulating gate, have remained largely unchanged, even as transistors are miniaturized to sizes of 10 nanometres. We investigated what dimensionally scalable logic technology beyond CMOS could provide improvements in efficiency and performance for von Neumann architectures and enable growth in emerging computing such as artifical intelligence. Such a computing technology needs to allow progressive miniaturization, reduce switching energy, improve device interconnection and provide a complete logic and memory family. Here we propose a scalable spintronic logic device that operates via spin-orbit transduction (the coupling of an electron's angular momentum with its linear momentum) combined with magnetoelectric switching. The device uses advanced quantum materials, especially correlated oxides and topological states of matter, for collective switching and detection. We describe progress in magnetoelectric switching and spin-orbit detection of state, and show that in comparison with CMOS technology our device has superior switching energy (by a factor of 10 to 30), lower switching voltage (by a factor of 5) and enhanced logic density (by a factor of 5). In addition, its non-volatility enables ultralow standby power, which is critical to modern computing. The properties of our device indicate that the proposed technology could enable the development of multigenerational computing.

Transistor technology scaling<sup>1-3</sup> has been enabled by controlling the conductivity of a semiconductor using an electric field applied across a high-quality insulating gate dielectric. This fundamental principle has remained largely unchanged since the seminal observations of Moore and Dennard et al.<sup>4,5</sup>. Yet in the past decade, transistor scaling has been enabled by direct improvements to the carrier transport  $^{1,6,7}$ , combined with superior electrostatic control<sup>1-3,8</sup>. In contrast to pure dimensional scaling<sup>5</sup>, new transistor technologies have necessitated the use of strain<sup>6</sup>, three-dimensional electrostatic gate control<sup>2,8</sup>, manipulation of the effective carrier mass and band structure, and the gradual introduction of new materials for interface and work function con- ${\rm trol}^9$ . Despite the successful scaling in the size of transistors, voltage and frequency scaling have slowed  $^{10}$ . Further decrease of voltage has been hampered by the Boltzmann limit of current control (60 mV for every change in current by a factor of 10 at room temperature). In response, a considerable effort to invent, demonstrate and benchmark beyond-CMOS devices got underway<sup>11–13</sup>. This effort includes alternative computing devices based on electron spin, electron tunnelling, ferroelectrics, strain and phase change 12,13 (see Methods for beyond-CMOS logic device options). However, a technologically suitable computational logic device that has superior energy efficiency, high logic density (that is, computed functions per unit area), non-volatility (to counteract leakage power) and efficient interconnects has remained elusive. The importance of these considerations has become evident during extensive modelling, benchmarking and evaluation of more than 25 beyond-CMOS device proposals<sup>12,13</sup>. With these considerations in view, we propose and demonstrate the building blocks for a new logic device that enables (1) voltage scaling, (2) scalable interconnects, (3) energy scaling and (4) the potential for multi-generational dimensional scaling.

# Beyond-CMOS devices for replacing or enhancing the electronic transistor

Collective state switching devices are potential candidates for replacing or enhancing transistors. A collective state switch operates by the reversal of the material's order parameter (such as ferromagnetism, ferroelectricity and ferrotorodicity)<sup>13</sup> from  $\theta$  to  $-\theta$ . It addresses sub-10-nm miniaturization by using collective order parameter dynamics, overcoming the 'Boltzmann tyranny', which is inherent to conductivity modulation, and providing a non-volatile nature to the computer. It is well documented that the 'Boltzmann tyranny' and leakage are the central challenges in traditional CMOS devices<sup>1,2</sup>. Logic based on collective state switching devices is a leading option for computational advances beyond the modern CMOS era owing to its (1) potential for superior energy per operation, (2) higher computational logical density and efficiency (that is, fewer devices required per combinatorial logic function) owing to the use of majority gates<sup>14</sup>, (3) non-volatile memory-in-logic and logic-in-memory capability<sup>15</sup> and (4) amenability to traditional and emerging architectures (for example, neuromorphic<sup>16</sup> and stochastic computing<sup>17</sup>).

Among these possible collective state order parameters, ferroelectricity and multiferroicity are the preferred collective states for computing 13 owing to (1) the presence of a controllable, localized and phenomenologically strong carrier, the spontaneous dipole; (2) the switching efficiency of a ferroelectric with respect to the stability of the switch is given by the energy barrier per unit volume,  $\lambda = E_{\rm sw}/\Delta E(\Theta)$ , where  $\Delta E(\Theta)$  is the energy barrier relative to the stable state and  $E_{\rm sw}$  is the total energy dissipated in switching; lower values of  $\lambda$  enable computing switches to operate at lower energies for a given energy barrier.

A vital consideration for a new technology is the need for highly compact nanoscale interconnects. While ferroelectric switching and the

<sup>1</sup>Components Research, Intel Corporation, Hillsboro, OR, USA. <sup>2</sup>Intel Labs, Intel Corp., Santa Clara, CA, USA. <sup>3</sup>Department of Materials Science and Engineering, University of California, Berkeley, Berkeley, CA, USA. <sup>4</sup>Lawrence Berkeley National Laboratory, Berkeley, CA, USA. <sup>5</sup>Department of Physics, University of California, Berkeley, CA, USA. <sup>6</sup>e-mail: sasikanth.manipatruni@intel.com

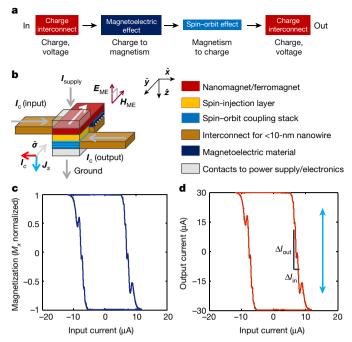

Fig. 1 | MESO logic transduction and device operation. a, Transduction of state variables for a cascadable charge-input and charge-output logic device. The magnetoelectric effect transduces the input information to magnetism, and the spin-orbit effect in a topological material transduces the magnetic state variable back to charge. b, MESO device formed with a magnetoelectric capacitor and a topological material. The device comprises a spin-injection layer for spin injection from the ferromagnet to the topological material, an interconnect made of a conductive material, and contacts to the power supply and ground. The logical state of the charge input (current in the +x direction) is inverted by the operation shown to charge output (current in the -x direction). Power for energy gain is injected from the power supply (arrows). Transduction mechanisms are calculated with magnetoelectric-vector SPICE models (see Methods and Supplementary Information). The white arrow represents the magnetization direction of the ferromagnet. Grey arrows represent electric currents at the input and output, power supply and ground. Injection of the power supply current allows for energy gain, large signal gain and the ability to drive larger output devices. c, Magnetoelectric transfer function, showing conversion of the charge input to ferromagnetic magnetization. d, Spin-orbit transfer function, showing conversion of a state to charge output. The response of the device is indicated for small signal gain (black line) and the full signal range ( $-15 \,\mu\text{A}$  to  $15 \,\mu\text{A}$ ; blue arrow). See Supplementary Fig. 1 for the two operating states of the MESO inverter device.

accompanying magnetoelectric switching of ferromagnets are perhaps the most energy-efficient charge-driven switching phenomena at the nanoscale and at room temperature, an efficient way to read out the state has been lacking. The discovery of strong spin–charge coupling in topological matter via a Rashba–Edelstein or topological two-dimensional electron gas<sup>18–25</sup> enables this proposal for a charge-driven, scalable logic computing device.

# Spin-orbit logic device with magnetoelectric input signal nodes

We propose a logic computing device with magnetoelectric switching nodes and spin-orbit-effect readout operating at 100 mV, with an electrical interconnect. The magnetoelectric spin-orbit (MESO) device comprises two technologically scalable transduction mechanisms: ferroelectric/magnetoelectric switching<sup>26-30</sup> and topological conversion of spin to charge<sup>19-24</sup>. The device interfaces with electrical interconnects and is therefore charge-/voltage-driven and produces a charge/voltage output (Fig. 1a). The MESO device (Fig. 1b) comprises a magnetoelectric switching capacitor, a ferromagnet and a spin-to-charge conversion module (see 'Material requirements for

1–10-aJ-class MESO logic'). In Fig. 1b, when the input interconnect carries a positive current (current flowing in the +x direction), an electric field is set up in the magnetoelectric capacitor in the -z direction (into the plane). The resulting magnetoelectricity (represented as an effective field  $H_{\rm ME}$ ), which may be comprised of an electrically controlled exchange bias or exchange anisotropy, switches the nanomagnet to the -y direction (see Supplementary Information section A for details).

The readout (detection) of the state of the switch is enabled by the ongoing advances in spin-to-charge conversion using topological or high-spin-orbit-coupling (SOC) materials. A supply current is injected into the device, causing a flow of spin-polarized electrons from the ferromagnet into the SOC material. Owing to SOC spin-to-charge transduction (Fig. 1b), a charge current is generated at the output, in this case in the -x direction. Hence, the input charge state (positive voltage and current) is inverted by the MESO logic gate at the output.

We applied spin/magnetoelectric circuit theory<sup>31,32</sup> (see Supplementary Information section B) combined with stochastic magnetization dynamics solvers<sup>32</sup> (see Supplementary Information sections C and D) to obtain the transfer characteristics of the MESO logic device. We further used rigorous integrated-circuit solvers to validate and benchmark against spin-logic examples (Supplementary Information sections E and F). SPICE (simulation program with integrated circuit emphasis) circuit solvers were developed to incorporate the effects of: (1) magnetoelectric switching, (2) all the energy sources and dissipation elements (Supplementary Information sections G and H), (3) Landau-Khalatnikov dynamics of ferroelectric switching (Supplementary Information section I) and (4) peripheral charge circuitry (Supplementary Information section J). Details on simulations of energy scaling to <10 aJ  $(1 \text{ aJ} = 10^{-18} \text{ J})$  using the power boundary method and component-level energy calculations are presented in Supplementary Information section K. The MESO inverter transfer functions, with magnetic and electric hysteresis, are shown in Fig. 1c, d. The input current  $I_{in}$  of the magnetization transfer function (Fig. 1c) relates the magnetoelectric stimulus with magnetization switching. It shows a small-signal gain  $(d\hat{m}/dI_{in})$ , where  $\hat{m}$  is the magnetic moment unit vector for the nanomagnet's magnetization), which is advantageous for noise rejection. A large-signal gain of the output current,  $I_{\text{out}}$  (ratio  $I_{\text{out}}/I_{\text{in}}$ ) is generated and controlled by the supply current ( $I_{\text{supply}}$ ). A small-signal gain ( $dI_{\text{out}}/dI_{\text{in}}$ ) of the device during switching can be seen in Fig. 1d. We show a scheme of the proposed short-/long-range interconnect in Fig. 2a, where the charge output of one MESO stage drives a charge current to switch the input of the next MESO stage<sup>32,33</sup>. Bidirectional logic switching of a cascaded six-stage MESO inverter chain is described in Supplementary Information section L.

#### Transduction mechanisms for the MESO device

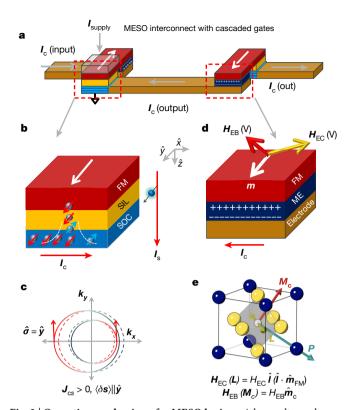

We identified a scalable way to transduce the spin state of a nanomagnet to a charge state via spin–orbit effects  $^{19-26,33-36}$ , such as the interface Rashba–Edelstein effect (IREE) and spin-momentum locking in topological insulators. It has recently been shown that spin currents can be converted to charge currents that preserve the information encoded in spin polarization  $^{34-37}$  (using resonant spin pumping in the quasi-static non-local spin-valve configuration  $^{33}$ ). Figure 2b shows how a current through a nanomagnet produces injection of spin-polarized electrons into a stack composed of materials with a high SOC coefficient (for example, Bi/Ag<sup>22,37</sup>, topological insulators  $^{21,24,34,35}$ , oxides and two-dimensional materials  $^{25,36}$ ). In Fig. 2b, when  $\hat{\boldsymbol{m}}$  is pointing in the  $\hat{\boldsymbol{y}}$  direction and the flow of the injected spin current is  $\boldsymbol{J}_s = \boldsymbol{J}_s \hat{\boldsymbol{z}}$ , with injected spin polarization along the  $+\boldsymbol{y}$  direction, charge current  $\boldsymbol{I}_c$  is generated in the  $\hat{\boldsymbol{x}}$  direction. When the nanomagnet reverses to the  $-\hat{\boldsymbol{y}}$  direction and the flow of injected spin current is still  $\boldsymbol{J}_s = J_s \hat{\boldsymbol{z}}$ , but with injected spin polarization along the  $-\boldsymbol{y}$  direction, a charge current  $\boldsymbol{I}_c$  is generated in the  $-\hat{\boldsymbol{x}}$  direction. Hence, the magnetization direction of the nanomagnet is transduced into the direction of the electric current.

Fig. 2 | Operating mechanisms for MESO logic. a, A low-voltage-chargebased MESO interconnect with cascaded logic gates. Two inverters are chained together to form an interconnect. Arrows show the directions of the input and output currents of the device. Materials are as in Fig. 1. b, Operating mechanism for spin-to-charge conversion using a high-SOC material (SOC). A spin injection layer (SIL) is used where needed by the materials' interfaces. Spins injected from the ferromagnet (FM) in the +zdirection with spin polarization along the +y (in-plane) direction cause a topologically generated charge current in the SOC layer. Small red and blue arrows indicate up and down spins, respectively, injected from the magnet. The large red arrows show the directions of the charge  $(I_c)$  and injected spin  $(I_s)$  currents. c, Schematic of the k-space for spin-to-charge conversion at a two-dimensional electron gas with high SOC. Injecting a spin current polarized along the +y direction overpopulates the Fermi surface on one side of the topological material compared to the other side. This generates a net charge current in the x direction. The conversion has the right symmetry to convert the information of the ferromagnet to the charge current output. The dashed and solid lines depict the Fermi surface of the material before and after spin injection, respectively. Injected spin density  $\langle \delta \mathbf{s} \rangle$  along the +y direction leads to charge current  $J_{cs} > 0$ . d, Operating mechanism for a magnetoelectric (ME) material. A ferromagnet is coupled via exchange/strain to the magnetoelectric material.  $H_{\rm EB}$  and  $H_{\rm EC}$  are the exchange bias and the exchange coupling from the magnetoelectric material to the ferromagnet, respectively, and *m* is the magnetization of the ferromagnet. **e**, A classic multiferroic– magnetoelectric material, BiFeO<sub>3</sub>, is shown with the order parameters: polarization (P), antiferromagnetism (L) and weak canted magnetization  $(M_c)$ . The electric-field setup in a generic magnetoelectric/ferroelectric material produces exchange bias, coupling and anisotropy modulation for magnetostrictive effects. Yellow and blue spheres depict Bi and Fe atoms in a canonic room-temperature multiferroic BiFeO<sub>3</sub>.  $\hat{\boldsymbol{m}}_{\text{FM}}, \hat{\boldsymbol{m}}_{\text{c}}$  and  $\hat{\boldsymbol{l}}$  represent the unit vectors of magnetization of the coupled layer, the magnetization of the canted spins and the antiferromagnetic axis, respectively. In general, the magneto-electric field generates an exchange coupling along the axial direction of  $\hat{I}$ , the AFM axial direction and exchange bias, the direction of weak ferromagnetism  $\hat{m}_c$ .

The spin–orbit mechanism responsible for spin-to-charge conversion at the interface is described by the Hamiltonian

$$H_{\rm R} = \alpha_{\rm R} \left( \boldsymbol{k} \times \hat{\boldsymbol{z}} \right) \cdot \hat{\boldsymbol{\sigma}} \tag{1}$$

where  $\alpha_{\rm R}=(k_{\rm F+}-k_{\rm F-})\hbar^2/2m$  is the Rashba coefficient ( $\hbar$  is the Planck constant),  $k_{\rm F+}$  and  $k_{\rm F-}$  are the Fermi vectors of the two spin-split bands,  $\hat{z}$  is the unit vector normal to the interface,  $\hat{\sigma}$  is the vector of the Pauli spin matrices and k is the momentum of the electrons. In a simple model based on two Fermi contours in the Rashba electron gas (Fig. 2c), the density of spin polarization along the y axis,  $\delta s_{y\pm}$  (Fig. 2b, c), and the charge current density along the x axis,  $j_{\rm cx\pm}$ , can be related as  $^{20,23}$

$$\delta s_{y\pm} = \pm \frac{m}{2e\hbar k_{\rm F,\pm}} j_{\rm cx\pm} \tag{2}$$

which yields the relation between spin density (per unit area) and charge current (per unit width) in a two-dimensional Rashba electron gas:

$$j_{\rm cx} = \frac{e\alpha_{\rm R}}{\hbar} \langle \delta s \rangle_y = \frac{\alpha_{\rm R} \tau_{\rm s}}{\hbar} j_{\rm sy} = \lambda_{\rm IREE} j_{\rm sy} \tag{3}$$

where the relation between spin current and spin polarization is determined by the spin relaxation time  $\tau_s$  as  $j_s = e\delta s/\tau_s$ , where e is the electron charge. For a pure helical ground state in topological systems,  $\lambda_{\text{IREE}} = V_F \tau$ , where  $V_F$  is the Fermi velocity and  $\tau$  is the relaxation time for the spin distribution at an out-of-equilibrium interface. This results in the generation of a charge current in the interconnect that is proportional to the spin current (Fig. 2c). The transduction relates the linear charge current density  $j_{cx}$  (in units of ampere per metre) and the areal spin current density  $j_{sy}$  (spin current flowing along the z direction, comprised of spins oriented along the y direction; in units of ampere per square metre); see Supplementary Information section M and Supplementary Fig. 16.

Magnetoelectricity provides a highly energy-efficient mechanism for logic switching with intrinsic switching energy given by

$$E_{\rm ME} = 2P_{\rm s}V_{\rm c} \tag{4}$$

where  $P_s$  is the switched polarization and  $V_c$  the critical voltage for switching. To the best of our knowledge, magnetoelectric/ferroelectric switching is the most energy-efficient mechanism at room temperature that scales to lateral dimensions of 10 nm and retains a stable collective order parameter. The switching mechanism for magnetoelectric switching of a ferromagnet is shown Fig. 2d, and a canonical room-temperature multiferroic magnetoelectric (BiFeO<sub>3</sub>) is illustrated in Fig. 2e. In general, magnetoelectric switching can be accomplished by coupling the ferroelectricity/ferroelasticity to antiferromagnetism and/or a weak canted magnetic moment. The intrinsic switching energy for ferroelectric/magnetoelectric switching can approach 1 aJ per bit (about 30 times lower than the switching energy of advanced CMOS devices) by scaling the switched polarization to about  $10 \,\mu\text{C} \,\text{cm}^{-2}$  and switching voltages to 100 mV (Please see Supplementary Fig. 24 for lowvoltage ferroelectric characterization of SRO/20 nm LBFO/SRO heterostructure). Both of these metrics are within the reach of experimental room-temperature materials (as shown in Table 1).

#### Miniaturization and scaling laws for MESO logic

We now derive and apply the scaling laws for magnetoelectric and spinorbit transductions. For spin-to-charge conversion using inverse SOC (ISOC), the efficiency improves with reducing the width of the magnet, a highly desirable scaling feature. In the presence of topological coupling between spin and charge states in a Rashba system, we can write

$$I_{c} = \frac{1}{w} \lambda'_{ISOC} (\hat{\boldsymbol{\sigma}} \times I_{s})$$

(5)

where w is the width of the magnet (the minimum feature size for the device), where  $\lambda'_{\rm ISOC}$  is the effective SOC conversion length. The recent discovery of two-dimensional high-SOC systems indicates that the effective  $\lambda_{\rm IREE}$  can be as high as 6 nm in Bi<sub>2</sub>Se<sub>3</sub><sup>34,35</sup> and LaAlO<sub>3</sub>/SrTiO<sub>3</sub><sup>25,36,38</sup>. To assess the suitability of spin–orbit logic for progressive

Table 1 | Device and material targets to enable 1-10-aJ-class MESO logic

|                  | Device figure of merit                     | Nominal target                       | Material figures of merit                           | Nominal target (for 1–10 aJ per switch)                             |

|------------------|--------------------------------------------|--------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------|

| SOC materials    | Spin-to-charge conversion, $I_c/I_s$       | >50%                                 | $\lambda_{IREE}$                                    | >5 nm <sup>25,35,36,38</sup>                                        |

|                  | Source resistance                          | $>$ 10 k $\Omega$                    | Resistivity                                         | $> 10 \ m\Omega$ cm (refs $^{25,26,35,36,38}$ )                     |

| Magnetoelectrics | Dimensions                                 | ${<}10\times10\times10\text{nm}^{3}$ | Charge/area (for 1–10 aJ target)                    | $0.5-5~\mu C~cm^{-2}~(ref.~^{42})$                                  |

|                  | Equivalent capacitance/area                | ${<}100~\text{fF}~\mu\text{m}^{-2}$  | Coercive field                                      | $100{\text{-}}500 \text{ kV cm}^{-1} \text{ (refs}^{27,30}\text{)}$ |

|                  | Switching voltage                          | 0.1 – 0.3 V                          | Magnetoelectric coefficient, $\alpha_{\mathrm{ME}}$ | $10  \mathrm{C}^{-1}$ (refs $^{27,28}$ )                            |

|                  | Write error rate                           | $< 10^{-12}$                         | Reliability                                         | >10 <sup>15</sup>                                                   |

| Interconnect     | Resistance/ length                         | $0.15~k\Omega~\mu m^{-1}$            | Resistivity                                         | $4200\mu\Omega$ cm at $10\text{nm}$ width $^3$                      |

|                  | Capacitance/ length                        | $10100~\text{aF}\mu\text{m}^{-1}$    | Interlayer dielectric (dielectric constant)         | 1–10 (ref. <sup>3</sup> )                                           |

|                  | Peak currents                              | 10–100 μA per magnet                 | Electromigration limit                              | $>$ 25 MA cm $^{-1}$ at 10 nm width                                 |

| Nanomagnet       | Size                                       | $20\text{nm}\times30\text{nm}$       |                                                     |                                                                     |

|                  | Magnetic stability (barrier, $\Delta/kT$ ) | 40                                   | Magnetization, M <sub>s</sub>                       | $<$ 500 MA cm $^{-1}$                                               |

|                  | Spin injection                             | >80%                                 | Spin polarization                                   | >80%                                                                |

miniaturization (Moore's law), we show that the energy required to switch the device decreases with dimensional scaling of the device. This can be attributed to an improvement in the spin-to-charge conversion efficiency,  $\eta_{\rm SOC}$ , with a reduction in the width  $W_{\rm FM}$  of the nanomagnet  $(\eta_{\rm SOC} \propto 1/W_{\rm FM})$  and a reduction in the switched charge of the magnetoelectric/ferroelectric node, Q, with areal scaling  $(Q \propto W_{\rm FM}^2)$ . The energy required to switch a single MESO logic unit is given by

$$\begin{split} E_{\text{MESO}} &= E_{\text{CME}} + E_{\text{IC}} + E_{\text{ISOC}} + E_{\text{RT}} + E_{\text{SG}} \\ &= C_{\text{me}} V_{\text{me}}^2 \left( 1 + \alpha \frac{W_{\text{FM}}}{\lambda'_{\text{SOC}}} \right) \end{split} \tag{6}$$

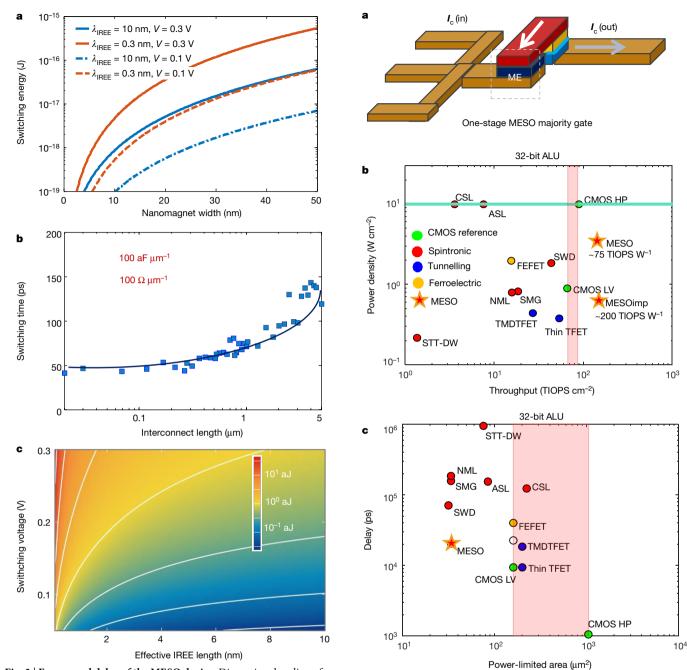

$C_{\mathrm{me}}$  is the equivalent capacitance,  $V_{\mathrm{me}}$  is the switching voltage and  $\alpha$  is the conversion factor. (see Supplementary Information sections G–K for detailed analytical and numerical energy calculations of the intrinsic magnetoelectric energy,  $E_{\mathrm{CME}}$ , interconnect losses,  $E_{\mathrm{IC}}$ , and losses in the spin-to-charge conversion layer,  $E_{\mathrm{ISOC}}$ , in the driving electronics,  $E_{\mathrm{RT}}$ , and in the supply–ground path,  $E_{\mathrm{SG}}$ ). Figure 3a shows the strong, cubic scaling of the MESO energy ( $E_{\mathrm{MESO}}$ ), where the energy is reduced by a factor of 8 for every reduction by a factor of 2 in feature size. The excellent scalability of MESO logic allows the switching energy of the MESO logic to approach 1 aJ per bit. Magnetoelectric switching also allows strong voltage scaling in energy per bit, where progressive voltage reduction enables lowering of the switching energy. Figure 3c shows a combination of scaling in energy/switching via voltage and effective IREE length towards the 0.1–10 aJ range.

## Low-voltage (100 mV) charge interconnects for scaling below 10 nm

We now address one of the most demanding aspects of new computing technology: the interconnects that connect the devices at the nanoscale  $^{39,40}$ . MESO logic can address the interconnect scaling problem, which has emerged as a major limitation when the width of the electrical wires reached  $<\!20$  nm. Experimental data for highly scaled interconnects show that the resistivity of electrical wires increases according to the Mayadas–Shatzkes scaling law  $^{41}$

$$\rho = \rho_0 \left[ 1 + \frac{3\lambda_{\text{ebulk}}}{8t} \left( 1 + \frac{p}{2} \right) + \frac{3\lambda_{\text{ebulk}}}{2D} \left( \frac{r}{1 - r} \right) \right] \tag{7}$$

(where  $\rho_0$  is the bulk resistivity,  $\lambda_{\rm ebulk}$  is the electron mean free path, p is the specularity, r is the reflection parameter from grain boundaries, t is the thickness of the film and D the grain size) as the critical interconnect dimensions approach the electron mean free path. A second scaling issue with electrical interconnects is the high capacitance per unit length. Hence, it is of great interest to demonstrate a logic technology compatible with high-resistivity and high-capacitance interconnects.

MESO logic enables the development of a low-voltage charge interconnect that is amenable to highly scaled integrated circuits that comprise wires of 10-30 nm width. We show that MESO logic can tolerate the use of nanometallic interconnects with high resistivity (>1 m $\Omega$  cm; a 20-100-times less stringent requirement for the conductance of smallwidth interconnect material) and capacitance (>10 fF  $\mu$ m<sup>-1</sup>; a 100-times less stringent requirement for the capacitance of the interconnects); see Supplementary Information section N. Figure 3b shows the dependence of switching time on the interconnect length at a metal resistivity of 100  $\mu\Omega$  cm and an effective 30 nm  $\times$  30 nm cross-sectional area of 900 nm<sup>2</sup>. The switching speed of the MESO device scales linearly with interconnect length up to 1,000 nm at a line resistance of 100  $\Omega$   $\mu$ m<sup>-1</sup> and a capacitance of  $100~\text{aF}\,\mu\text{m}^{-1}$  (see Supplementary Information section N). This would represent a substantial relaxation in the requirements placed on nanometallic interconnects compared to CMOS devices. This is in contrast to spin interconnects, where the signal, and thus the switching speed, degrade as  $\exp(-x/L_{\rm sf})$ , where  $L_{\rm sf}$  is the spin-flip length and x is the direction of transport. Hence, MESO logic alleviates the traditional problem of interconnects used for spin logic and allows continued scaling of metallic and semiconducting wires.

When compared with the leading beyond-CMOS and highly scaled advanced CMOS technologies, the MESO device provides sizeable gains in areal logic density, energy of operation and computational throughput. In Fig. 4a, we compare the energy delay and the logic density (area per function) of MESO logic with leading beyond-CMOS transistor technologies and highly scaled advanced CMOS devices. The majority logic gate, a universal gate that (together with NOT) can implement all Boolean logic functions, is used to build complex spinlogic functions, such as a 32-bit adder or a 32-bit arithmetic logic unit (ALU)<sup>12</sup>, with the results shown in Fig. 4b (also see Supplementary Information section F). The proposed MESO logic device enables competitive energy delay performance compared to leading beyond-CMOS devices, while also allowing non-volatility. The MESO logic device enables considerable improvement compared to other spintronic devices owing to magnetoelectric switching. Gains in the delay are due to the use of electrical (rather than spin-based) interconnects and very compact majority-gate circuits (see Fig. 4c). The MESO device also enables energy reduction compared to CMOS logic operating at very low (0.3 V) supply voltages, owing to its ability to switch at even lower supply voltages (0.1 V). The speed of MESO logic units is comparable to that of low-power, low-leakage CMOS devices (0.3 V supply voltage). We note that at a low logic activity factor and intermittent usage, the non-volatility of the MESO device can offer further advantages compared to CMOS devices by eliminating standby power dissipation and enabling instant operation from standby. Figure 4c shows the advantage of the MESO device in terms of areal logic density compared to advanced CMOS technology.

Fig. 3 | Energy and delay of the MESO device. Dimensional scaling of MESO logic shows improvement in switching energy as the devices get smaller. a, Cubic scaling with magnet width. b, Effect of the length of the interconnect (30 nm  $\times$  30 nm cross-section) on the (inverter) device performance, obtained from interconnect modelling of the MESO device. See Supplementary Information for the effects of the capacitance and length on device performance. We simulated the interconnect with  $100~\Omega~\mu m^{-1}$  resistance and  $100~aF~\mu m^{-1}$  capacitance per unit length. c, Intrinsic switching energy of MESO (colour bar) with improvements in switching voltage and SOC strength (effective IREE length).

## Experimental progress on magneto-electrics and spin-orbit transduction

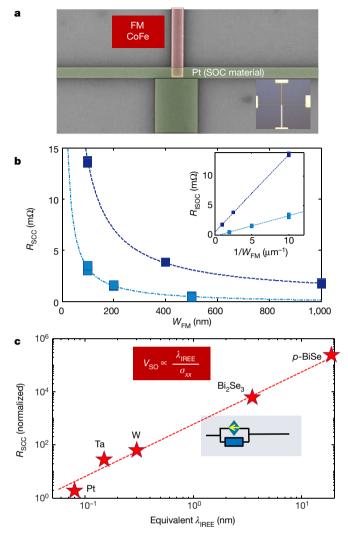

We now turn to the initial experimental manifestations of the two central concepts of the MESO device and conclude with a summary of innovations required to meet the MESO target of 100 mV and 1 aJ per bit. First we demonstrate a local-spin-injection device in which spin-polarized charge current  $I_s$  is injected from the ferromagnet (CoFe) into a spin-orbit material (Pt) (see Supplementary Information section P for the fabrication method and the device cross-section).

Fig. 4 | Performance and area of MESO device in comparison with advanced CMOS and leading beyond-CMOS devices. a, Scheme of a MESO majority logic gate used for benchmarking. **b**, Power per unit area versus throughput (that is, number of 32-bit ALU operations per unit time and unit area, in units of tera-integer operations per second; TIOPS) for CMOS and beyond-CMOS devices. The constraint of a power density not higher than 10 W cm<sup>-2</sup> is implemented, when necessary, by inserting an empty area into the optimally laid out circuits. c, Delay of 32-bit ALU operation versus the power-limited area for CMOS and beyond-CMOS devices. Power-limited area comprehends the increase in area of the computational logic to meet the power density contraint of 10 W cm<sup>-2</sup> in **b**. STT-DW, spin-transfer-torque domain-wall device; ASL, all-spin-logic device; CSL, charge spin logic; NML, nanomagnetic logic; SMG, spin majority gate; SWD, spin wave device; CMOS HP, high-performance CMOS at 0.73 V supply; CMOS LV, low-power CMOS operating at 0.3 V supply; FEFET, ferroelectric FET; Thin TFET, 2D-material vertical tunnel FET; TMDTFET, transition-metal dichalcogenide tunnel FET; see Methods.

An open-circuit charge voltage  $V_{\rm oc}$  that depends on the spin polarization of the injected spin current is measured across the Pt wire. The equivalent spin-to-charge-conversion resistance ( $R_{\rm SCC} = V_{\rm oc}/I_{\rm s}$ ) is plotted in

Fig. 5 | Spin–orbit readout for the MESO device. a, A proof-of-concept device for a spin–orbit readout mechanism in which a spin in a polarized charge current is passed into a spin–orbit material (Pt) from a CoFe ferromagnet. The inset shows a microscope image of the device. b, Charge readout of the spin state of the ferromagnet, measured using a non-local resistance (lateral voltage divided by vertical current). Shown are measured data from devices with various CoFe width and fixed Pt width of 100 nm (dark blue) and 400 nm (light blue). The inset shows linear fits to  $1/W_{\rm FM}$ . c, Projected improvement in the spin–orbit readout through the use of topological insulators with low conductivity and high spin–orbit effects.  $V_{\rm so}$  and  $\sigma_{xx}$  are the generated voltage and conductivity, respectively.

Fig. 5b. To study the dimensional scaling of the device, we measured  $R_{\rm SCC}$  with two sets of test devices. Figure 5b shows measured data from devices with various CoFe widths  $W_{\rm FM}$ . Test chip A (dark-blue line with Pt width 100 nm) comprises five different device geometries with dimensions  $W_{\rm FM}=100$  nm, 100 nm, 400 nm, 1,000 nm and 1,000 nm and test chip B (light-blue line with Pt width is 400 nm) has five different device geometries with dimensions  $W_{\rm FM}=100$  nm, 100 nm, 200 nm, 200 nm, 500 nm and 500 nm. We observe a dimensional scaling law, in accordance with the above expression for SOC spin-to-charge conversion; see inset for a linear fit to  $1/W_{\rm FM}$ . The equivalent spin-to-charge conversion resistance scales favourably for high-resistivity topological materials as  $R_{\rm SCC} \propto \lambda_{\rm IREE}/\rho$ . For high-resistivity spin-orbit systems (see Table 1) we expect that  $R_{\rm SCC}$  can be enhanced considerably. Combined with the areal scaling of the magnetoelectric capacitor, this provides a total device energy scaling of  $W_{\rm FM}^3$ .

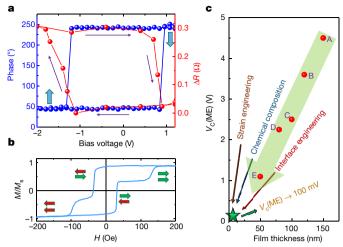

To illustrate the past year's remarkable progress in magnetoelectric transduction, we present in Fig. 6a–c representative magnetoelectric switching data of a CoFe/Cu/CoFe spin valve that is exchange-coupled

Fig. 6 | Progress of magnetoelectric transduction via MESO towards a voltage of 100 mV. a, Piezoelectric loop (blue) and applied-voltagedependent resistance modulation ( $\Delta R$ ; red) of a Pt/CoFe/Cu/CoFe/LBFO/ LSMO magnetoelectric spin-valve device depict 1 V magnetoelectric switching. The vertical axis shows the phase of the ferro-electric polarization response signal with respect to the input voltage. Purple arrows indicate the sweep direction in the measurement. b, Magnetization  $M_{\rm s}$  of a giant magnetoresistive stack, normalized with the magnetization M of a thin film, as a function of magnetic field strength H. The bottom CoFe electrode of the giant magnetoresistive stack is exchange-coupled to LaBiFeO<sub>3</sub>, showing exchange-induced anisotropy enhancement and exchange bias. c, Voltage scaling of magnetoelectric switching as a function of multiferroic film thickness. Data points A-D correspond to BiFeO<sub>3</sub> films of varying thickness with a SrRuO<sub>3</sub> bottom electrode. The switching voltage of the MESO device  $V_c(ME)$  is lowered down to 1.0 V using partial chemical substitution of Bi<sup>3+</sup> (with La<sup>3+</sup>), interface engineering (electrodes formed with  $La_{0.7}Sr_{0.3}MnO_3$ ) and thickness scaling down to 40 nm. The ultimate goal of the MESO project is to be able to switch magnetoelectrically at 100 mV.

to a 45-nm-thick La<sub>0.1</sub>Bi<sub>0.9</sub>FeO<sub>3</sub> (LBFO) layer using an applied voltage of only 1–2 V—although quasi-static ferroelectric switching has been achieved down to about 150 mV using LBFO as the magnetoelectric layer (see Supplementary Information section Q for details). Figure 6a shows the change in the resistance of the CoFe/Cu/CoFe spin valve as a function of voltage applied across the multiferroic LBFO thin film, along with the piezoelectric loop of the (CoFe/Cu/CoFe)/LBFO/LSMO capacitor structure. It is clear that both ferroelectric and concurrent magnetoelectric switching occur at about 1.0 V. This is enabled by the strong exchange coupling of the bottom CoFe layer of the CoFe/Cu/ CoFe spin valve to the canted antiferromagnetic LBFO surface, which is evident from the magnetic hysteresis loop in Fig. 6b. Such an exchangebias coupling can be reversed by an out-of-plane electric field. Figure 6c shows how rapidly this switching voltage has been decreasing over the past year, primarily through materials engineering of the switching behaviour of the BiFeO<sub>3</sub> layer, as well as through systematic thickness reductions. The ferroelectric saturation polarization and the switching voltage of BiFeO<sub>3</sub> can be tuned by the doping level of the rare-earth element, such as La or Sm<sup>42</sup>. The potential for further reductions in the switching voltage is illustrated through the quasi-static piezoelectric switching loop of a 20-nm-thick LBFO layer in contact with symmetric SrRuO<sub>3</sub> top and bottom electrodes, demonstrating a switching voltage of 130-150 mV (see details in Supplementary Information section Q). Further reductions in the switching voltage, which is the immediate focus of our research, should be possible through reduction of the LBFO film thickness and further careful tuning of the composition such that the polar distortion is delicately tuned to be as low as possible. Independent work by our group and others has shown that both the ferroelectric and antiferromagnetic orders are stable down to at least a few nanometres (see Supplementary Information). A proof of concept for an ultralow-switching-voltage ferroelectric ( $La_xBi_{1-x}FeO_3$ )

Table 2 | Material options for MESO logic

|                                                 | Type 1                                                                                                                                            | Type 2                                                                                                        | Type 3                                                                                           |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| SOC materials for spin-<br>to-charge conversion | High-SOC and topological oxides                                                                                                                   | Topological materials and superlattices                                                                       | Two-dimensional transi-<br>tion-metal dichalcogenides                                            |

|                                                 | Bi <sub>2</sub> O <sub>3</sub> <sup>44</sup> , SrIrO <sub>3</sub> <sup>45</sup> , SrTiO <sub>3</sub> /LaAlO <sub>3</sub> <sup>25,36,38</sup>      | ${\sf Bi_{1.5}Sb_{0.5}Te_{1.7}Se_{1.3}}^{24}, {\sf Bi_2Se_3}^{34,35}, \alpha\text{-Sn}^{46}, {\sf BiSb}^{47}$ | $MoS_2^{48}$ , $MX_2^{49}$                                                                       |

| Magneto-electrics                               | Multiferroics                                                                                                                                     | Magnetostrictive                                                                                              | Exchange bias                                                                                    |

|                                                 | $\begin{array}{l} \text{BiFeO}_3^{27,30}, \text{LaBiFeO}_3^{42}, \text{TbMnO}_3^{50}, \text{LuFeO}_3/\\ \text{LuFe}_2\text{O}_4^{51} \end{array}$ | $Fe_3Ga^{52}$ , $Tb_xDy_{1-x}Fe_2^{53}$ , $FeRh^{28}$                                                         | Cr <sub>2</sub> O <sub>3</sub> <sup>29,54</sup> , Fe <sub>2</sub> TeO <sub>6</sub> <sup>55</sup> |

| Interconnect                                    | Noble metals                                                                                                                                      | Metal-semiconductor                                                                                           | Interlayer dielectric                                                                            |

|                                                 | Cu, Ag, Co, Al, Ru                                                                                                                                | poly-Si, NiSi, CoSi, NiGe, TiSi                                                                               | SiO <sub>2</sub> , SiN, SiCOH, polymers                                                          |

| Nanomagnet                                      | Nominal ferromagnets                                                                                                                              | Heusler alloys                                                                                                |                                                                                                  |

|                                                 | Co, Fe, Ni, CoFe, NiFe                                                                                                                            | $X_2YZ$ and $XYZ$ alloys (for example, $Co_2FeAI$ , $Mn_3Ga$ )                                                |                                                                                                  |

Three classes of materials (high-SOC oxides, topological materials and superlattices, and two-dimensional transition-metal dichalcogenides) are suitable for SOC-based spin-to-charge conversion. Magnetoelectrics belong to three classes: (1) multiferroics with magnetic (antiferromagnetic/ferromagnetic) and electric (ferroelectric) order parameters, (2) magnetostrictive, that is, one ferromagnetic-order-parameter material combined with a strain/piezoelectric material, and (3) exchange-bias materials, that is, one magnetic-order parameter with no ferroelectric/antiferroelectric order. Magnetostrictive materials are not directly suitable (because only 90° switching is feasible), but can be used to enhance magnetoelectric switching. Interconnect options comprise noble metals, metal-semiconductors (which exhibit excellent gap fill for interconnect processing and have short electron mean free paths) and interlayer dielectrics chosen for their low dielectric constant.

Nanomagnets should be conductive to allow spin injection with the applied bias. Co-, Fe- and Ni-based ferromagnets or Heusler alloys are potential candidates, with low M<sub>s</sub> and high spin polarization.

was obtained using symmetric conductive-oxide electrodes (SrRuO<sub>3</sub>), from which the switching energy was estimated to be about 1 aJ per bit for a contact area of  $10~\text{nm} \times 10~\text{nm}$ .

#### Material requirements for 1-10-aJ-class MESO logic

We describe the material scaling requirements for 1-10-aJ-class MESO logic scalable to critical dimensions of <10 nm or device density beyond 10<sup>10</sup> cm<sup>-2</sup>. In Table 1 we summarize the material scaling requirements for four classes of materials: a) SOC materials for spin-to-charge conversion, (2) magnetoelectrics for chargeto-spin conversion, (3) interconnects scalable to nanoscale widths and (4) nanomagnets. We considered the experimental values shown for the inverse Rashba-Edelstein parameters. A large-signal magnetoelectric coefficient of  $10c^{-1}$  (c, speed of light) from magnetoelectric switching and low coercive voltages were obtained via rhombohedral distortion tuning and chemical substitution of multiferroics<sup>42</sup> with thickness scalability to 5–20 nm. The output resistance of the ISOC spin current source is a critical parameter that affects the driving ability of the MESO logic device (high source resistance is preferred for a current source; see Supplementary Information section H and Supplementary Fig. 9.) The requirement of low interconnect resistivity is considerably relaxed owing to the low-voltage, low-current operation of chargemediated magnetoelectric logic. This is reflected in the resistivity target of 4–200  $\mu\Omega$  cm, which is comparable to the resistivity of scaled metal wires. Electromigration of the metal interconnect imposes a challenging limit on the switching speed by limiting the peak current in wires. MESO logic relaxes the electromigration requirements to 25 MA cm<sup>-2</sup> appreciably below the Belch limit for electromigration of interconnect metal candidates<sup>43</sup>.

A focused effort using quantum materials can enable logic technology operating at 100 mV and 1 aJ per bit. The details of four fundamental material classes are presented in Table 2. SOC materials can be comprised of (1) high-SOC oxides (for example, W(O) and Bi<sub>2</sub>O<sub>3</sub><sup>44</sup>) and oxides with strong topological effects (SrIrO<sub>3</sub><sup>45</sup> and SrTiO<sub>3</sub>/LaAlO<sub>3</sub><sup>25,36,38</sup>), (2) topological materials (Bi<sub>1.5</sub>Sb<sub>0.5</sub>Te<sub>1.7</sub>Se<sub>1.3</sub><sup>24</sup>, Sn-Bi<sub>2</sub>Te<sub>2</sub>Se, Bi<sub>2</sub>Se<sub>3</sub><sup>34,35</sup>,  $\alpha$ -Sn<sup>46</sup>, BiSb<sup>47</sup>) and their superlattices and (3) transition-metal dichalcogenides with large spin-orbit effects (MoS<sub>2</sub><sup>48</sup>  $MX_2^{49}$ ). The magnetoelectric materials can be comprised of (1) multiferroics with coupling of the antiferromagnetic and ferroelectric orders (type -1 multiferroics BiFeO<sub>3</sub><sup>27,30</sup> and LaBiFeO<sub>3</sub><sup>42</sup>; type-2 multiferroics, such as TbMnO<sub>3</sub><sup>50</sup>; and improper multiferroics, such as LuFeO<sub>3</sub>/ LuFe<sub>2</sub>O<sub>4</sub><sup>51</sup>), (2) magnetostrictive materials (Fe<sub>3</sub>Ga<sup>52</sup>, Tb<sub>x</sub>Dy<sub>1-x</sub>Fe<sub>2</sub><sup>53</sup>, FeRh<sup>18</sup>) and (3) electrically tuned exchange-mediated magnetoelectrics  $(Cr_2O_3^{29,54} \text{ or } Fe_2TeO_6^{55})$ . The interconnect options scalable to dimensions smaller than the 10 nm critical width can be based on transition metals (Cu, Ag, Co, Al, Ru) or their semiconductor alloys (poly-Si,

NiSi, CoSi, NiGe, TiSi), combined with low-interconnect-capacitance materials (SiO $_2$ , SiN, SiCOH, polymers). The nanomagnetic materials can be ferromagnets/ferrimagnets (Co, Fe, Ni, CoFe, NiFe, and X $_2$ YZ and XYZ alloys, such as Co $_2$ FeAl, Mn $_3$ Ga), in which a wide range of saturation magnetization and magnetic anisotropy are feasible to meet the dimensionality and retention requirements. In each of these four classes of materials, considerable development is required to improve the material interfaces for integrated devices, the operating temperature range, the processing temperature compatibility and, most importantly, the performance metrics.

#### Conclusion

In conclusion, we propose a scalable beyond-CMOS spintronic logic device with non-volatility and an energy-efficient charge-based interconnect. The proposed device allows (a) continued scaling in energy per operation towards attojoule-level switching energy (about 30 times below that of advanced CMOS devices) at 100 mV (more than 5 times below the operating voltage of advanced CMOS devices), (2) substantial improvement in logic density (about 5 times compared to advanced CMOS devices), enabled by majority-gate circuits implemented with a collective switching device, (3) improved scalability for interconnects due to the small impact of the resistivity, which is up to 1 m $\Omega$  cm, and (4) a path to seamless monolithic integration with CMOS technology (see Supplementary Fig. 19). The development of a beyond-CMOS device with an advantageous scaling method using quantum materials, highly compact majority logic<sup>14</sup> and non-volatile logic<sup>15</sup> can open up a potentially new technology paradigm for improving energy efficiency in beyond-CMOS computing devices. Combined with non-volatility and ultra-low energy, MESO logic may enable entirely new computer architectures that may avoid the trade-offs of the Turing and von Neumann architectures and of Amdahl's law. A combination of quantum materials, novel integration and new logic architectures may thus enable computing beyond advanced CMOS technology.

#### Online content

Any methods, additional references, Nature Research reporting summaries, source data, statements of data availability and associated accession codes are available at https://doi.org/10.1038/s41586-018-0770-2.

Received: 24 April 2016; Accepted: 7 October 2018; Published online 3 December 2018.

- Kuhn, K. J. Considerations for ultimate CMOS scaling. IEEE Trans. Electron Dev. 59, 1813–1828 (2012).

- Ferain, I., Colinge, C. A. & Colinge, J.-P. Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors. *Nature* 479, 310–316 (2011).

### RESEARCH ARTICLE

- Auth, C. et al. A 10 nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, self-aligned quad patterning, contact over active gate and cobalt local interconnects. In *Electron Devices Meeting* 2017, 29.1.1–29.1.4 (IEEE, 2017).

- Moore, G. E. Cramming more components onto integrated circuits. Proc. IEEE 86, 82–85 (1998).

- Dennard, R. H., Gaensslen, F. H., Yu, H. N., Rideout, V. L., Bassous, E. & Leblanc, A. R. Design of ion-implanted MOSFET's with very small physical dimensions. *IEEE J. Solid St. Circ.* 9, 256–268 (1974).

- Ghani, T. et al. A 90 nm high volume manufacturing logic technology featuring novel 45nm gate length strained silicon CMOS transistors. In *Electron Devices Meeting* 2003, 11.6.1–11.6.3 (IEEE, 2003).

- Krishnamohan, T. et al. Comparison of (001), (110) and (111) uniaxial- and biaxial- strained-Ge and strained-Si PMOS DGFETs for all channel orientations: mobility enhancement, drive current, delay and off-state leakage. In *Electron Devices Meeting* 2008, 1–4 (IEEE, 2008).

- Huang, X. et al. Sub 50-nm FinFET: PMOS. In Electron Devices Meeting 1998, 67–70 (IEEE, 1999).

- Schumacher, M., Baumann, P. K. & Seidel, T. AVD and ALD as two complementary technology solutions for next generation dielectric and conductive thin-film processing. *Chem. Vap. Depos.* 12, 99–108 (2006).

- Horowitz, M. Computing's energy problem (and what we can do about it). In Solid-State Circuits Conference Digest of Technical Papers 2014 10–14 (IEEE, 2014).

- Theis, T. N. & Solomon, P. M. It's time to reinvent the transistor! Science 327, 1600–1601 (2010).

- Nikonov, D. E. & Young, I. A., Benchmarking of beyond-CMOS exploratory devices for logic integrated circuits. *IEEE J. Explor. Solid-State Computat. Devices Circuits* 1, 3–11 (2015).

- Manipatruni, S., Nikonov, D. E. & Young, I. A. Beyond CMOS computing with spin and polarization. Nat. Phys. 14, 338 (2018).

- Zografos, O. et al. Design and benchmarking of hybrid CMOS-spin wave device circuits compared to 10 nm CMOS. In 2015 IEEE 15th International Conference on Nanotechnology (IEEE-NANO), 686–689 (IEEE, 2015).

- Ma, K. et al. Nonvolatile processor architecture exploration for energyharvesting applications. *IEEE Micro* 35, 32–40 (2015).

- Mead, C. Neuromorphic electronic systems. Proc. IEÉE 78, 1629–1636 (1990).

- Patil, A. D., Manipatruni, S., Nikonov, D., Young, I. A. & Shanbhag, N. R. 2017. Shannon-inspired statistical computing to enable spintronics. Preprint at https://arxiv.org/abs/1702.06119 (2017).

- Dyakonov, M. I. & Perel, V. I. Current-induced spin orientation of electrons in semiconductors. Phys. Lett. A 35, 459 (1971).

- Edelstein, V. M. Spin polarization of conduction electrons induced by electric current in two-dimensional asymmetric electron systems. *Solid State Commun.* 73, 233–235 (1990).

- Soumyanarayanan, A., Reyren, N., Fert, A. & Panagopoulos, C. Emergent phenomena induced by spin-orbit coupling at surfaces and interfaces. *Nature* 539, 509 (2016).

- Hsieh, D. et al. A tunable topological insulator in the spin helical Dirac transport regime. Nature 460, 1101 (2009).

- Rojas Sánchez, J. C. et al. Spin-to-charge conversion using Rashba coupling at the interface between non-magnetic materials. *Nat. Commun.* 4, 2944 (2013).

- Shen, K., Vignale, G. & Raimondi, R. Microscopic theory of the inverse Edelstein effect. *Phys. Rev. Lett.* 112, 096601 (2014).

- Shiomi, Y. et al. Spin–electricity conversion induced by spin injection into topological insulators. Phys. Rev. Lett. 113, 196601 (2014).

- Varignon, J., Vila, L., Barthelemy, A. & Bibes, M. A new spin for oxide interfaces. Nat. Phys. 14, 322 (2018).

- Spaldin, N. A. & Fiebig, M. The renaissance of magnetoelectric multiferroics. Science 309, 391–392 (2005).

- 27. Heron, J. T. et al. Deterministic switching of ferromagnetism at room temperature using an electric field. *Nature* **516**, 370–373 (2014).

- 28. Cherifi, R. O. et al. Electric-field control of magnetic order above room temperature. *Nat. Mater.* **13**, 345–351 (2014).

- 29. He, X. et al. Robust isothermal electric control of exchange bias at room temperature. *Nat. Mater.* **9**, 579–585 (2010).

- Manipatruni, S. et al. Voltage control of uni-directional anisotropy in ferromagnet–multiferroic system. Preprint at https://arxiv.org/abs/ 1801.08280 (2018).

- Brataas, A., Bauer, G. E. & Kelly, P. J. Non-collinear magnetoelectronics. Phys. Rep. 427, 157–255 (2006).

- Manipatruni, S., Nikonov, D. E. & Young, I. A. Modeling and design of spintronic integrated circuits. *IEEE Trans. Circuits Syst.* 59, 2801–2814 (2012).

- Omori, Y. et al. Inverse spin Hall effect in a closed loop circuit. Appl. Phys. Lett. 104, 242415 (2014).

- Fan, Y. et al. Magnetization switching through giant spin-orbit torque in a magnetically doped topological insulator heterostructure. *Nat. Mater.* 13, 699 (2014).

- 35. Mahendra, D. C. et al. Room-temperature perpendicular magnetization switching through giant spin-orbit torque from sputtered Bi,Se(1–x) topological insulator material. Preprint at https://arxiv.org/abs/1703.03822 (2017).

- Lesne, E. et al. Highly efficient and tunable spin-to-charge conversion through Rashba coupling at oxide interfaces. Nat. Mater. 15, 1261–1266 (2016).

- Ast, C. R. et al. Giant spin splitting through surface alloying. Phys. Rev. Lett. 98, 186807 (2007).

- Veit, M. J., Arras, R., Ramshaw, B. J., Pentcheva, R. & Suzuki, Y. Nonzero Berry phase in quantum oscillations from giant Rashba-type spin splitting in LaTiO<sub>3</sub>/ SrTiO<sub>3</sub> heterostructures. *Nat. Commun.* 9, 1458 (2018).

- Meindl, J. D., Chen, Q. & Davis, J. A. Limits on silicon nanoelectronics for terascale integration. *Science* 293, 2044–2049 (2001).

- Manipatruni, S., Lipson, M. & Young, I. A. Device scaling considerations for nanophotonic CMOS global interconnects. *IEEE J. Sel. Topics Quantum Electron*. 19, 8200109 (2013).

- Mayadas, A. F., Shatzkes, M. & Janak, J. F. Electrical resistivity model for polycrystalline films: the case of specular reflection at external surfaces. *Appl. Phys. Lett.* 14, 345–347 (1969).

- Chu, Y. H. et al. Low voltage performance of epitaxial BiFeO<sub>3</sub> films on Si substrates through lanthanum substitution. *Appl. Phys. Lett.* 92, 102909 (2008)

- Gardner, D. S., Meindl, J. D. & Saraswat, K. C. Interconnection and electro migration scaling theory. *IEEE Trans. Electron Dev.* 34, 633–643 (1987).

- Karube, S., Kondou, K. & Otani, Y. 2016. Experimental observation of spin to charge current conversion at non-magnetic metal/Bi<sub>2</sub>O<sub>3</sub> interfaces. Preprint at https://arxiv.org/abs/1601.04292 (2016).

- Pesin, D. & Balents, L. Mott physics and band topology in materials with strong spin-orbit interaction. Nat. Phys. 6, 376 (2010).

- Rojas-Sánchez, J.-C. et al. Spin to charge conversion at room temperature by spin pumping into a new type of topological insulator: α-Sn films. *Phys. Rev. Lett.* 116, 096602 (2016).

- Khang, N. H. D., Ueda, Y. & Hai, P. N. A conductive topological insulator with large spin Hall effect for ultralow power spin-orbit torque switching. *Nat. Mater.* 17, 808–813 (2018).

- Cheng, C. et al. Direct observation of spin-to-charge conversion in MoS<sub>2</sub> monolayer with spin pumping. Preprint at https://arxiv.org/abs/1510.03451 (2015).

- Wang, G. et al. Spin-orbit engineering in transition metal dichalcogenide alloy monolayers. Nat. Commun. 6, 10110 (2015).

- Kimura, T., Goto, T., Shintani, H., Ishizaka, K., Arima, T. & Tokura, Y. Magnetic control of ferroelectric polarization. *Nature* 426, 55–58 (2003).

- Mundy, J. A. et al. Atomically engineered ferroic layers yield a roomtemperature magnetoelectric multiferroic. Nature 537, 523 (2016).

- Srisukhumbowornchai, N. & Guruswamy, S. Large magnetostriction in directionally solidified FeGa and FeGaAl alloys. J. Appl. Phys. 90, 5680–5688 (2001).

- Ryu, J., et al. Magnetoelectric properties in piezoelectric and magnetostrictive laminate composites. *Jpn J. Appl. Phys.* 40, 4948 –4951 (2001).

- Street, M. et al. Increasing the Néel temperature of magnetoelectric chromia for voltage-controlled spintronics. Appl. Phys. Lett. 104, 222402 (2014).

- Wang, J. et al. Magnetoelectric Fe<sub>2</sub>TeO<sub>6</sub> thin films. J. Phys. Condens. Matter 26, 055012 (2014).

Acknowledgements We are grateful to A. Fert and J.-P. Wang for discussions. We acknowledge F. Rana, D. Schlom and F. Casanova for insights shared with us. We also acknowledge the support of K. Oguz and B. Buford of Intel Corporation for discussions on device integration and metrology. R.R. acknowledges the long-term support of the Quantum Materials programme funded by the US Department of Energy, Office of Basic Energy Sciences, which laid the foundation for the key elements of the work reported in this paper. B.P., Y.-L.H. and R.R. acknowledge support from Semiconductor Research Corporation within the JUMP program.

**Reviewer information** *Nature* thanks V. Bertacco, Y. Otani and the other anonymous reviewer(s) for their contribution to the peer review of this work.

Author contributions S.M. identified the use of the inverse spin-orbit effect for electrically transduced spin-logic devices. S.M., D.E.N. and I.A.Y. developed the logic circuits. S.M. developed the scaling laws, physical macro models and interconnect estimates. H.L. developed circuit design techniques and performed the logic-circuit simulations with the physical macro models. S.M. and R.R. developed the material scaling options and coordinated the material growth. S.M. conceptualized the test devices and designed the experiments and measurements for the magnetoelectric and spin-orbit devices. D.E.N. benchmarked the performance of the circuits. C.-C.L., B.P. and T.G. performed the layout of the test devices, processed the devices and identified processing methods for sub-micron-sized magnetoelectric and spin-orbit devices. S.M. and E.B. measured the magnetoelectric devices. S.M. and T.G. measured the spin-orbit devices. B.P., Y.-L.H. and E.B. deposited the samples and performed material characterization under the supervision of R.R. S.M. wrote the manuscript and D.E.N., I.A.Y. and R.R. edited the manuscript. All authors reviewed the manuscript and interpreted the data.

Competing interests The authors declare no competing interests.

#### Additional information

**Supplementary information** is available for this paper at https://doi.org/10.1038/s41586-018-0770-2.

Reprints and permissions information is available at http://www.nature.com/reprints

**Correspondence and requests for materials** should be addressed to S.M. **Publisher's note:** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

#### **METHODS**

Uniform benchmarking to beyond-CMOS logic options. We adopted the uniform, beyond-CMOS benchmarking method <sup>12</sup> to compare beyond-CMOS options. This method describes the impact of material improvements, device parameters, circuit topology and interconnects on the performance of computing devices. The model is adopted in beyond-CMOS research and includes the following spin-logic devices: (1) spin-torque devices<sup>32,56-58</sup> (spin-transfer-torque domain-wall device, all-spin-logic device, charge spin logic, spin-torque oscillator logic), (2) dipolefield devices (nanomagnetic logic)<sup>59</sup>, and (3) magnetoelectric devices (MESO, spin majority gate, spin-wave device<sup>60</sup>). We evaluated several digital logic circuits <sup>12</sup> (a fanout-4 inverter, a two-input NAND adder, a 32-bit ripple-carry adder and a 32-bit ALU) to compare the MESO logic with leading beyond-CMOS logic options. We also considered tunnelling field-effect transistors<sup>61,62</sup>, ferroelectric and piezoelectric integration in transistors<sup>63,64</sup> and Mott transistors<sup>65</sup>. See Supplementary Information section F, for a detailed explanation of the benchmarking.

**Vector spin circuit modelling of MESO logic.** We verify the functionality of MESO spin logic using an equivalent spin circuit model that describes the magnetization dynamics of the nanomagnet, vector spin injection, spin-to-charge transduction and magnetoelectric switching. The equivalent circuit model is based on vector spin circuit theory (magnetoelectric circuit analysis); see Supplementary Information section B.

The intrinsic resistance of the ISOC current source is derived from the conductivity of the interconnect and the ISOC conversion layers. The nanomagnet is connected to a control transistor operating as a power supply and shared among several MESO devices. We have also included the resistance and capacitance parasitics of the ground contact. The conductance across the magnet to the spin injection layer is modelled as a  $4\times 4$  matrix that relates the four-component charge and spin voltages to the injected four-component charge and spin currents  $^{31,32,66}$ . The current injected at the nanomagnet–ferromagnet interface is given by

$$\begin{bmatrix} I_c \\ I_{sx} \\ I_{sy} \\ I_{sz} \end{bmatrix} = R^{-1}(\hat{\boldsymbol{m}}) \begin{bmatrix} G_{11} & \alpha G_{11} & 0 & 0 \\ \alpha G_{11} & G_{11} & 0 & 0 \\ 0 & 0 & G_{SL} & G_{FL} \\ 0 & 0 & -G_{FL} & G_{SL} \end{bmatrix} R(\hat{\boldsymbol{m}}) \begin{bmatrix} V_N - V_F \\ V_{sx} \\ V_{sy} \\ V_{sz} \end{bmatrix}$$

(3)

where R is the rotation matrix that accounts for the magnetization direction of the nanomagnet, and  $I_{si}$  and  $V_{si}$ ,  $i = \{x, y, z\}$ , are the components of the spin current and voltage, respectively.  $G_{\rm SL}$ ,  $G_{\rm FL}$ ,  $G_{\rm 11}$ ,  $V_{\rm N}$  and  $V_{\rm F}$  are the conductance elements for the Slonczewski torque, field-like torque, conductance, voltage at the normal metal and voltage at the ferromagnet, correspondingly. See Supplementary Information sections B and C for a detailed explanation of the model.

Stochastic behaviour of magnetoelectric switching versus spin-torque switching. We modelled the magnetization dynamics of the nanomagnet using the Landau–Lifshitz–Gilbert equation  $^{50}$  and the Fokker–Planck equation  $^{67,68}$ . The modified Landau–Lifshitz–Gilbert equation, a phenomenological equation that describes the dynamics of a nanomagnet with magnetic moment unit vector  $\hat{\boldsymbol{m}}$ , was used for Monte Carlo simulations (see Supplementary Table 1 for parameters). We used the Fokker–Planck equation for uniaxial anisotropy parameterized with the angle of the magnetization, which was validated versus the Monte Carlo simulations of the nanomagnets. See Supplementary Information sections C and O for a detailed explanation of the stochastic modelling,

Complete logic family and state elements. The proposed device family is readily extended to a general-purpose computing state machine. A state machine and complete Boolean logic family are the prerequisites for a Turing machine<sup>69</sup>. Majority logic operation can be readily demonstrated because the input of a capacitive node is added to the charge currents converging at the node via the Kirchhoff law. Spin-logic devices with multiple switching inputs (domain-wall, spin-wave or spin-current) have been shown to facilitate the development of majority logic<sup>70</sup>

and spin state machines<sup>71</sup>. Combined with a random access memory (RAM), a state machine enables general-purpose computing.

CMOS compatibility, memory and control logic. The proposed magnetoelectric-logic scalable spintronic logic device has several desirable features that are compatible with CMOS nanoelectronics. First, the MESO device can be integrated in the backend of the CMOS process (that is, between the interconnect layers), allowing CMOS devices to be used for clocking, control and power supply (Supplementary Fig. 19). Second, MESO devices can serve as elements of an embedded memory with 'logic-compatible speed' (known as large-signal memory, commonly implemented with a static RAM), making them usable as on-chip non-volatile memories. Third, the MESO device allows stacking of several layers of magnetic logic in a three-dimensional architecture. Fourth, because the state variable of the interconnect between MESO gates is the charge, MESO logic can be readily interfaced with CMOS circuitry to implement clocking control and power delivery. Owing to its low supply voltage, the MESO device is efficient even with interconnects with high metal resistivity of  $>100~\mu\Omega$  cm<sup>72,73</sup>.

**Code availability.** The MATLAB codes used to benchmark the circuit performance are available under 'Benchmarking of devices' from the Nanoelectronics Research Initiative, at https://nanohub.org/tools/nribench/browser/trunk/src.

#### Data availability

The data that support the findings of this study are available from the corresponding author on reasonable request.

- 56. Behin-Aein, B., Datta, D., Salahuddin, S. & Datta, S. Proposal for an all-spin logic device with built-in memory. *Nat. Nanotechnol.* **5**, 266–270 (2010).

- Nikonov, D. E., Bourianoff, G. I. & Ghani, T. Proposal of a spin torque majority gate logic. *IEEE Electron Device Lett.* 32, 1128–1130 (2011).

- Manipatruni, S., Nikonov, D. E. & Young, I. A. Material targets for scaling all-spin logic. *Phys. Rev. Appl.* 5, 014002 (2016).

- Imre, A. et al. Majority logic gate for magnetic quantum-dot cellular automata. Science 311, 205–208 (2006).

- 60. Chumak, A. V., Serga, A. A. & Hillebrands, B. Magnon transistor for all-magnon data processing. *Nat. Commun.* **5**, 4700 (2014).

- Ionescu, A. M. & Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. *Nature* 479, 329–337 (2011).

- Lu, H. & Seabaugh, A. Tunnel field-effect transistors: state-of-the-art. IEEE J. Electron Devices Soc. 2, 44–49 (2014).

- Salahuddin, S. & Datta, S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. *Nano Lett.* 8, 405–410 (2008)

- Newns, D., Elmegreen, B., Liu, X. H. & Martyna, G. A low-voltage high-speed electronic switch based on piezoelectric transduction. *J. Appl. Phys.* 111, 084509 (2012).

- Son, J., Rajan, S., Stemmer, S. & Allen, S. J. A heterojunction modulation-doped Mott transistor. J. Appl. Phys. 110, 084503 (2011).

- Srinivasan, S., Diep, V., Behin-Aein, B., Sarkar, A. & Datta, S. Modeling multi-magnet networks interacting via spin currents. In *Handbook of Spintronics* 1281–1335 (2016).

- Apalkov, D. M. & Visscher, P. B. Spin-torque switching: Fokker–Planck rate calculation. *Phys. Rev. B* 72, 180405 (2005).

- Butler, W. H. et al. Switching distributions for perpendicular spin-torque devices within the macrospin approximation. *IEEE Trans. Magnet.* 48, 4684–4700 (2012).

- Shannon, C. E. A universal Turing machine with two internal states. Automata Stud. 34, 157–165 (1957).

- Amarù, L. et al. Majority logic synthesis. In Proc. International Conference on Computer-Aided Design 79 (ACM, 2018).

- Manipatruni, S., Nikonov, D. E. & Young, I. A. All-spin nanomagnetic state elements. Appl. Phys. Lett. 103, 063503 (2013).

- Dutta, S. et al. Highly scaled ruthenium interconnects. IEEE Electron Dev. Lett. 38, 949–951 (2017).

- Dutta, S. et al. Sub-100 nm<sup>2</sup> cobalt interconnects. *IEEE Electron Dev. Lett.* 39, 731–734 (2018).